)中起着首要的效用,它可能用于统制和统治电磁骚扰(EMI)以及抬高电子摆设的抗骚扰才力。以下是

1. 滤波器:电容常被用作滤波器的症结元件。正在电子摆设中,通过将电容安置正在信号线或电源线上,可能有用地滤除高频噪声和电磁骚扰,确保摆设的电源和信号线不受到外部电磁波的骚扰。

2. 电源解耦:正在电子电道中,电容被用作电源解耦器,以确保电子元件正在事情时得回安稳的电源。这有助于防备电源线上的噪声流传到症结的电子元件中。

3. 箝制射频骚扰:射频(RF)骚扰是一种高频骚扰,经常影响无线通讯摆设和其他高频电子摆设。电容可能被用来招揽和箝制这些射频信号,防备其进入或脱离摆设。

4. 防静电放电:正在某些境况中,静电放电或许对摆设酿成破坏。电容可能用于招揽和开释静电能量,从而减小静电对摆设的影响。

5. 差模噪声滤波:正在模仿电道中,电容经常用于差模信号的滤波,助助减小噪声对信号的影响。

6. 共模箝制:电容也被用于共模箝制电道,防备共模信号(即同时效用于两个电道导线的骚扰信号)对摆设酿成影响。

正在EMC策画中,电容的选型和结构长短常症结的。相宜的电容选拔可能明显抬高摆设的电磁兼容性,防备区别局限之间的彼此骚扰,同时确保摆设正在电磁境况中安稳运转。

咱们用来滤波的电容器并不是理念的电容器,正在体系中实践体现为理念电容与电感和电阻的串联。如图所示。

众层电容器(Muti-LayerCapacitor)正在装置到PCB板上时会形成快要5nH的寄生电感,再加上约30m欧的引线电阻,其频率特点体现为如图所示的弧线。滤波电容将不是理念的低通滤波器,实践的插入损耗特点体现为以自谐振点为核心的带通滤波电道。

两个电容串联时,因为ESL(等效串联电感)和ESR(等效串联电阻)的存正在,会形成反谐振题目。下图给出了电容并联的等效道理

正在快要15MHz到175MHz的一个较宽的频带内,并联电容的阻抗比单唯一个大电容的阻抗要来的大,因为两电容形成了谐振,正在150MHz处形成了一个阻抗的峰值,体系其他局限正在该频率局限内形成的能量只可有很少的一局限被旁道到地平面。

正在策画凡是电道时,工程师们经常合切的是电容的容值、耐压值、封装巨细、事情温度局限、温漂等参数。然则正在高速电道上或电源体系中及少少对电容哀求很高的时钟电道中,电容仍然不但仅是电容,是一个由等效电容、等效电阻和等效电感构成的一个电道,容易的机合如图所示。

图中,C为所需电容,ESR为等效串联电阻,ESL为等效串联电感,CP为等效并联电容。

既然这是一个电道,那么就不再是一颗独立电容那么容易了。这个等效电道功能受良众身分的影响,正在选拔这类电容时,不但仅要合切前面提到的那些参数,还要合切正在特定频率下的等效参数,以Murata的1μF的电容为例,正在谐振频率点时,对应的等效电容为602.625nF,等效电阻为11.5356mΩ,等效电感为471.621pH。理念电容和实践电容就外现出不相似的功能。如图所示是理念电容和实践电容的阻抗弧线。

正在工程执行中,良众工程师看到参考板策画或其他工程师策画的板子中有良众电容,感到本身的产物遵循他们的策画照搬就不肯定不会出题目。本来这也不是云云,由于产物使用区别、机合也有或许区别,这就或许使得产物策画的PCB层叠不相似、通流平面也不相似,而这些都是会惹起电源体系的不相似。

正在电源体系策画中,经常都邑有良众类型的电容存正在,如一个电源体系中会有100μF、47μF、22μF、10μF、1μF、0.1μF等类型的电容,这么众类型的电容是否可能同一为某一品种型的电容呢?如图所示,以电容的阻抗弧线为例,举行解释。

通过上面两张图比照可能看到,假如都操纵相像类型的电容,固然阻抗更低,然则去耦频率局限简直没转化;假如操纵区别品种的电容,则可能增大去耦频率局限。

正在电源体系中并不是电容越众越好,正在某些体系中假如电容众了反而会导致新的噪声点崭露。

并联电容的阻抗的峰值将会跟着ESR的减小而补充,并联谐振峰值的形式与地点取决于PCB板的策画与电容的选拔。

4、对付给天命目的电容器,比力好的选拔是电容值正在一个较大的局限内平均打开,各个电容值的ESR适中:比力差的选拔是仅有少量的电容值,并且电容的ESR都特地小。

电容的ESL与电容值一齐决心电容器的谐振点与并联电容器的反谐振点的频率局限。正在实践的策画中,应当尽量选用ESL小的电容器。

对付RF策画而言,陶瓷电容器、聚酯纤维电容器和聚苯乙烯薄膜电容器都是很好的选拔。对付EMI滤波器来讲,对电容器的介质资料哀求并不高,常睹的X7R、Y5V和Z5U等松散介质都是不错的选拔:经常绝对的电容值、电容器的温度系数、电压转化系数等并不首要。区别品种、区别容值的电容滤波局限是区别的,下面是样板的插入损耗比对恶果:

由上图可看出,同为0805封装的贴片陶瓷电容,001uF的电容比0.1uF的电容具有更好的高频

滤波特点;发起板极事情频率高于50MHz的单板(如传输、MUSA的众半单板)全体操纵0.01uF的滤波电容,而不是咱们目前大方采用的0.1uF的滤波电容。

咱们经常把电源模块输入、输出回道的电容称为滤波电容。容易阐明即是,保障输入、输出电源 安稳的电容。正在电源模块中,滤波电容摆放的准绳是“先大后小”。如图2.48.1所示,滤波电容按箭头 偏向先大后小摆放。

电源策画时,要留意走线和铜皮足够宽、过孔数目足够众,保障通流才力知足需求。宽度和过孔 数目贯串电流巨细来评估。

电源输入电容与开合环道酿成一个电流环。这个电流环道的转化幅度大,Iout的幅度。频率是开合频率。DCDC芯片开合流程中形成,这个电流环形成的电流的转化,蕴涵了较疾的di/dt。

同步BUCK的方法,续流旅途要源委芯片的GND管脚,输入电容要接正在芯片的GND和Vin之间,旅途尽或许短粗。

1、以供应商供给的产物材料上的自谐振特点为根蒂选拔电容,使之适当策画的时钟速度与噪声频率的须要。

2、正在所须要的频率局限内加尽或许众的电容。比如,22nF的电容的自谐振频率快要为11MHz,有效的阻抗(Z1欧姆)局限为6M~40MHz,你可能正在该频带局限内加尽或许众的电容,以到达须要退耦的水准。

3、正在尽或许迫近IC每个电源管脚的地方,起码放一个去耦电容器,以减小寄生阻抗。

4、旁道电容与IC尽或许放正在统一个PCB平面上。有一个须要格外留意的地方:正在两种结构中,Vcc收集都唯有一个点连到Vcc平面。云云做,使得IC外里的噪声都务必通过这个独一的过孔走到电源平面上去,过孔的附加阻抗助助避免了噪声向体系其余局限的扩散。

5、对付众时钟体系可能将电源平面作图3-14所示的瓜分,对每一个局限操纵一种确切容值的电容器,被狭缝隔离的电源平面将一局限的噪声与其他局限的敏锐器件隔离离来,同时供给了中容值的差别;

6、对付时钟频率正在一个较宽的局限内转化的体系,旁道电容的选拔甚为穷困。一个较好的管理步骤是将两个容值上亲昵2:1的电容并联安置,云云做可能供给一个较宽的低阻抗区,和一个较宽的旁道频率,下面这张图可能看到,阻抗峰值已经形成了,但却小于15欧,而可用的频率局限(阻抗小于15欧)则扩展到快要3.25MHz到100MHz的局限,这种众退耦电容的步骤只正在一个独立的IC须要一个较宽的旁道频率局限并且单个电容无法到达这一频带时才操纵。并且,容值务必保留2:1的局限内,以避免阻抗峰值领先可用的局限。

高速 IC的电源引脚须要足够众的去耦电容,最好能保障每个引脚有一个。实践策画中,假如没 有空间摆放去耦电容,则可能酌情删减。

IC 电源引脚的去耦电容的容值经常会比力小,如 0.1μF、0.01μF 等;对应的封装也比力小,如 0402封装、0603封装等。正在摆放去耦电容时,应留意以下几点。

(1)尽或许迫近电源引脚安置,不然或许起不到去耦效用。外面上讲,电容有肯定的去耦半径范 围,于是应肃穆实施就近准绳。

(2)去耦电容到电源引脚引线mm)。加粗方针正在于减小序线电感,保障电源功能。

(3)去耦电容的电源、地引脚从焊盘引出线后,就近打孔,相连到电源、地平面上。该引线同样要 加粗,过孔尽量用大孔,如能用孔径10mil 的孔,就不必8mil的孔。

(4)保障去耦环道尽量小。去耦电容常睹的摆放示比如图2.48.2~图2.48.4所示。图2.48.2~图2.48.4所示是SOP封装的IC 去耦电容的摆放方法,QFP等封装的与此仿佛。

常睹的 BGA封装,其去耦电容经常放正在 BGA下面,即反面。因为 BGA 封装引脚密度大,于是去 耦电容大凡放的不是良众,但应尽量众摆放少少,如图2.48.5所示。

储能电容可能保障正在负载神速变到最重时供电电压不会下跌。储能电容可分为板极储能电容、器件级储能电容两种:

A,板极储能电容:保障负载神速变到最重时,单板处处供电电压不会下跌。正在高频、高速单板(以及条目愿意的背板),发起平均排布肯定数目的较大容值的钽电容(luf、10uf、22uf、33uf),以保障单板统一电压的值保留相似。

B,器件级储能电容:保障负载神速变到最重时,器件界限处处供电电压不会下跌。对付事情频率、速度较高、功耗较大的器件,发起正在其界限排放1-4个较大容值的钼电容(luf、10uf、22uf、33uf),以保障器件神速变换时其事情电压保留褂讪。

1、当单板上具有众种供电电压时,对一种供电电压储能电容已经只选用一种容值的电容器,大凡选用外贴封装的Tantalum电容(钽电容),可能依据须要选拔10uf、22uf、33uf等;

2、区别供电电压的芯片组成一个群落,储能电容正在这个群落内平均散布,如下图所示:

储能电容的效用即是保障IC正在用电时,能正在最短的时候内供给电能。储能电容的容值大凡比力 大,对应的封装也比力大。正在PCB中,储能电容可能离器件远少少,但也不行太远,如图2.48.6所示。常睹的储能电容扇孔方法,如图2.48.7所示。

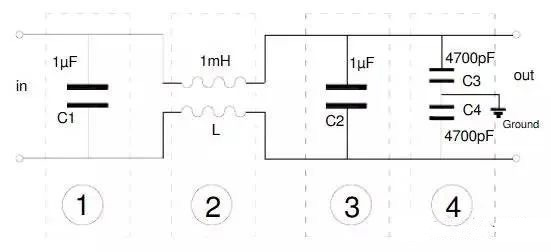

EMC滤波器经常指由 L,C组成的低通滤波器。区别机合的LC滤波器其区别正在于电容与电感的相连方法的区别。LC滤波器的有用性不但与其机合相合,并且还与相连收集的阻抗相合。如单个电容的滤波器正在高阻抗电道中恶果很好,而正在低阻抗电道中恶果很差。古板上,正在滤波器两头的端接阻抗为 50 欧姆的条目下刻画滤波器的特点,然则执行中源阻抗Zs和负载阻抗Zi又特地庞杂,而且它正在要箝制的频率点上或许是未知的。假如滤波器的一端或两头与电抗性元件相纠合,则有或许会形成谐振,使某些频率点的插入损耗变为插入增益。

如图所示,一信号通道中,L 与 C 构成一低通滤波电道,因为正在某一频点的源阻抗 Zs 和负载阻抗 Zi 不行知,正在操纵时咱们要避免参数组合后,将有效的频率因素滤掉。正在良众案例中,工程师往往比力青睐于操纵102,104 容值的电容,没有源委策动,有时或许拔苗助长。

经常电容的谐振是不会独立存正在的,大凡电容的自谐振是由电容与自己引脚的等效电感或相连电容的导线酿成的电感构成。咱们正在实践事情中依据策动公式可知:

串纠合构的LC正在发作谐振时,其两头阻抗最小,相当于短道;并纠合构的LC正在发作谐振时,两头阻抗最大,相当于开道。如图 1 所示, L与C正在形成谐振时,从信号流向解析(血色箭头所示),它是串联谐振,对付串联谐振电道的特点而言,相当于短道。假如LC的谐振频点正巧是咱们念要滤除的骚扰频点,那么L和C组成的通道相当于短道,就能很好地到达滤除噪声的方针。

比如正在这一信号通道中,此中有效频率为 5MHz,电道中的L值为 1uH,咱们要滤除其信号通道上10MHz的骚扰信号,就要避免补充的滤波电容C与L的谐振点落正在5MHz左近,从而将有效信号滤除。假如依据体验值选拔1000pF电容,通过上述谐振公式策动,策动出其谐振点为 5.03MHz,此时L C相当于短道,有效频率通过LC 直接到地,达不到咱们须要的恶果,反而使电道事情不服常。咱们应依据须要滤除的骚扰频率来选拔相宜的电容值,通过谐振频率公式代入策动,C 的取值为 253.3pF, 咱们取最亲昵值即可。还须要留意的是,假如用插脚元件,引脚要尽或许的短,假如或许最好选用贴片器件,其ESL最小。可睹,确切选拔滤波器的机合和元件参数至合首要。正在实践的电道应用中,体验值虽然首要,但正在某些园地下,体验值是不值得发起的,更加正在措置有效频率的谐波因素时,肯定要通过确切的步骤举行估算后再取值。

如图所示,要滤除线束上的噪声骚扰信号,优先选用低本钱的电容器,有时反而会将某些骚扰噪声引至其它旅途,从而形成天线效应,导致辐射巩固。选用电容时,要通晓地明确电容自己只起到能量的蜕变,而能量并未被花费,唯有将电容接至低阻抗收集时,才会到达滤波的恶果。正在执行事情中,电容反向蜕变的特点往往会被工程师们无视,行家都邑误以为地长久是纯净的,只须接地,都能管理题目,于是接地就成了整改工程师口中的全能良药。如下图所示

假设信号线dBm的电磁噪声须要滤除,经常环境下最先会念到用电容举行滤波措置,此时,电容须要蜕变的地,就肯定要被合切,地是否洁净,是否低阻,是否存正在地弹效应,是否会惹起环道效应等等。假设地上的噪声能量乃至比滤波对象的能量还要高,此时补充电容,即是会将地上的噪声反向蜕变至信号线上,信号线就成了最理念的辐射前言。

共模电容经常指的是差分信号中的共模电容,它是电道中一个首要的参数,格外是正在差分放大器和通讯体系中。

1.差模信号(Differential Mode Signal): 这是两个输入信号的不同局限,即两个信号的代数差。

2. 共模信号(Common Mode Signal): 这是两个输入信号的均匀值或协同局限。

共模电容指的是信号对地的共模局限的电容。这个电容对付少少电道来说或许是无益的,更加是正在差分放大器中。正在理念环境下,差分放大器只放大差模信号,而过错共模信号形成反映。然而,实践电道中总会存正在少少不完好,此中一个影响是共模电容。

大凡滤波器不独立操纵差模线圈,由于共模电感双方绕线不相似等源由,电感肯定不会相像,于是能起到肯定的差模电感的效用。假如差模骚扰比力吃紧,就要追加差模线圈。

可能看到,电容特点低频率高阻抗高频率低阻抗。滤波器运用电容正在高频时它的低阻抗短道掉差模千扰。(如图下图所示: )当频率为50Hz时,电容阻抗趋近于无尽大,相当于短道,不起任何衰减效用当频率为500kHz时,电容阻抗很小,依据上式可能看赴任模负载的电流衰减为趋近于0如当频率为500kHz时负载50欧容抗0.05欧。

此时电容分得了99.9%的差模骚扰电流,而负载只分得了0.1%的差模骚扰电流也即是说500kHz时,电容使得差模骚扰低重了30dB。